昨日在上海举办的首届 RISC-V 中国峰会上,中科院计算所宣布了一款开源的高性能 RISC-V 处理器 —— 香山。

香山是一款开源的高性能 RISC-V 处理器,基于 Chisel 硬件设计语言实现,支持 RV64GC 指令集。在香山处理器的开发过程中,团队使用了包括 Chisel、Verilator 等在内的大量开源工具,实现了差分验证、仿真快照、RISC-V 检查点等处理器开发的基础工具,建立起了一套包含设计、实现、验证等在内的基于开源 工具 的处理器前端敏捷开发流程。

据介绍,香山是中科院计算所牵头,多家企业联合开发的开源高性能 RISC-V 处理器核,源代码和所有设计文档均会开源。香山开源地址:https://github.com/OpenXiangShan/XiangShan。

示例视频

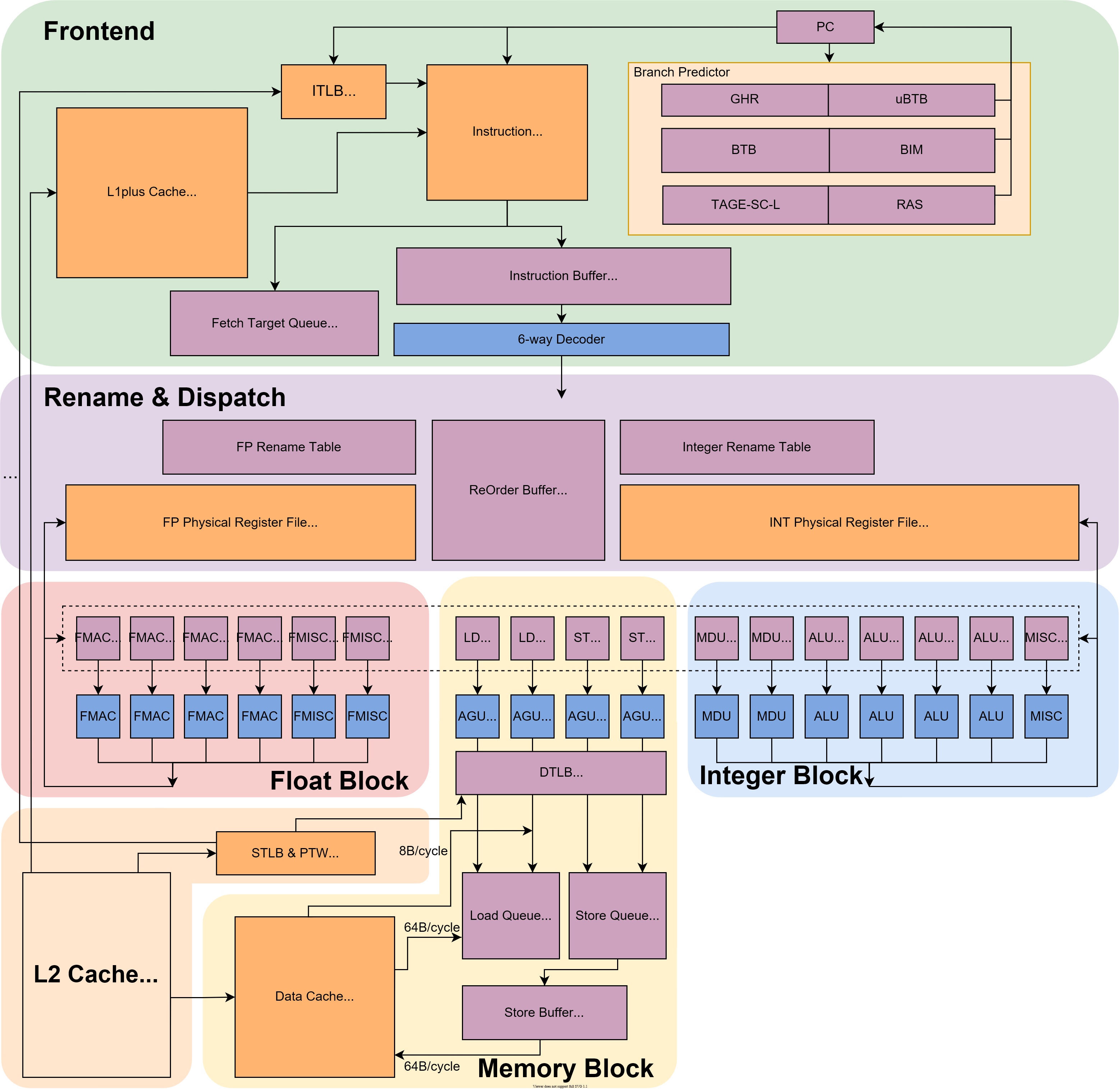

根据 PPT 的描述,香山的架构代号以湖命名。第一版架构代号是“雁栖湖”,“雁栖湖” RTL 代码于 2021 年 4 月完成,计划于 7 月基于 TSMC 28nm 工艺流片,目前频率为 1.3GHz,性能预估为 SEPC CPU2006 7分/Ghz。

▲ 第一版“雁栖湖”的微架构

第二版架构代号是“南湖”,“南湖”计划在今年年底流片,将采用中芯国际 14nm 工艺,目标频率是 2GHz,SPECCPU 分值达到10分/GHz。

香山采用木兰宽松版许可证 (MulanPSLv2),代码托管在 GitHub (https://github.com/OpenXiangShan/XiangShan),并同步镜像至 Gitee 等平台。

暂无回复。